This section suggested the typical design flow for task 1 based on past experience.

We aim to provide a brief guide for you to kick start. There are no right or wrong approach, (but could be poor approaches). The minor details are up to you to decide.

A. Theoretical Calculation

Based on the design specifications assigned to your team, decide what's the ideal range of the cutoff frequency.

B. Theoretical Design

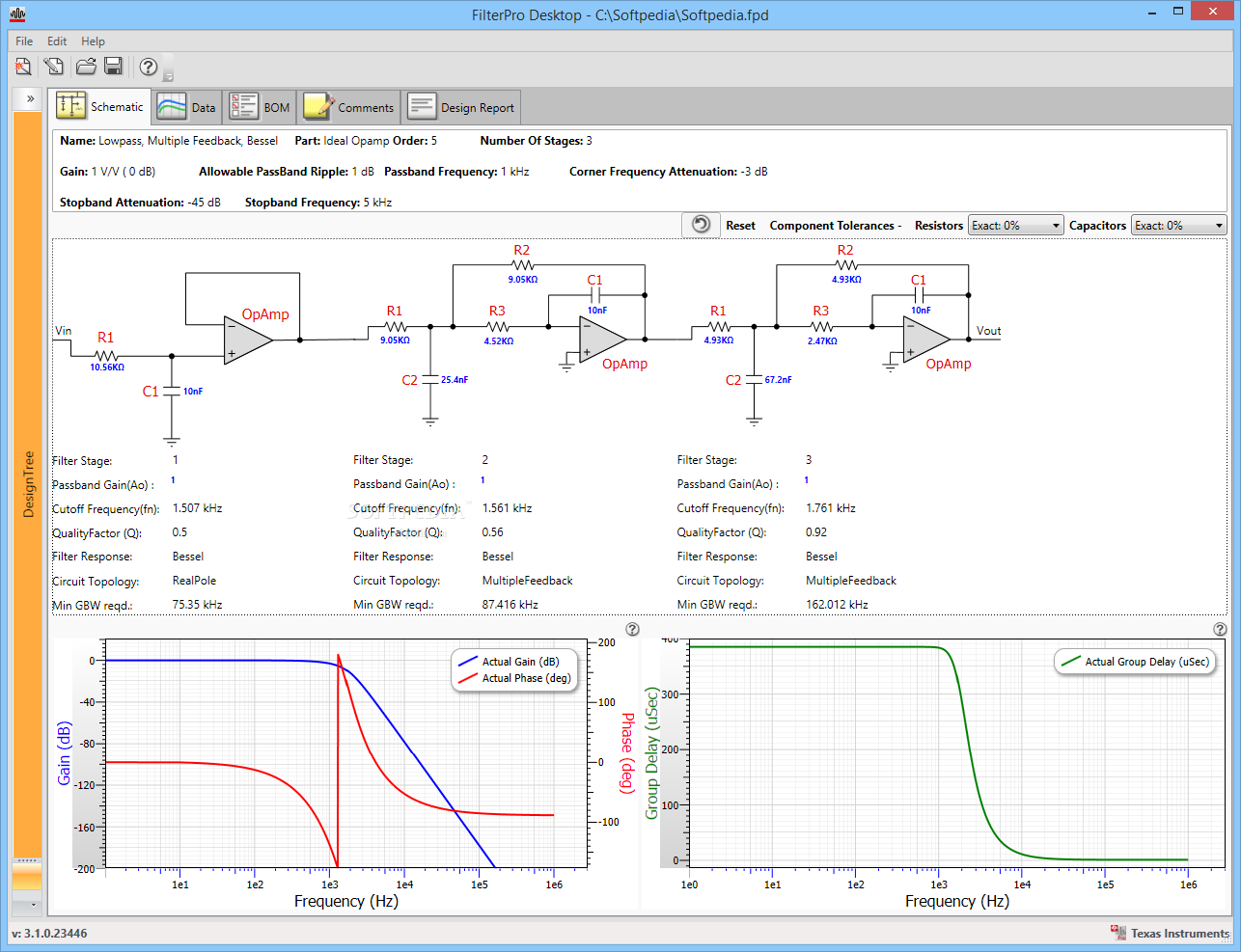

Based on the result from A, make use of FilterPro and generate your 1st theoretical Design.

Things you should spent time figuring out:

- How many orders/stages?

- Which response type to follow? What's the pros and cons?

- Do the provided OpAmps met the Min. GBW requirements? If no, what to do? (Refer to Lab 3)

Note: The Min. GBW requirement could be insanely large, this should hint you that this is an ideal design serves as a reference, our goal is NOT to duplicate it on the breadboard.

C.1. FilterPro Simulation (Frequency Response)

Implement the design generated in B with LTSpice.

Helpful guides for LTSpice can be found here.

Run AC simulation and plot the Bode Plot of the output from each stage, cross check the measured cutoff frequency with the designed cutoff frequency from B.

You may notice that the untuned filter circuit is not giving you what you expected, this is normal. This could be caused by various factors, you may put down your thoughts on this in your report.

Adjust R values to match the design. (Refer to Lecture Notes 3 final page for cutoff tuning)

C.2. FilterPro Simulation (Waveform)

FilterPro provides "realistic" simulation, once you've done tuning R in C.1., pass the recorded signal "sig.dat" through the LTSpice circuit, observe and save the output waveform as "test.dat".

Observe if distinguished HIGH and LOW with minimum noise spike is shown in the output waveform. (E.g., blue waveform in the above figure)

If no, repeat C.1. or consider redesign from section B.

If yes, pass the output waveform from LTSpice to GNURadio, "test.dat" serves as input of "opamp_file.grc". Run and observe the PSR count.

If you are satisfied with the PSR count at 1000 packet, you could move on to build the breadboard circuit now. If not, repeat C.1. or even redesign the filter.

D. Build and Test Breadboard Circuit

Based on your result of C.2., implement the circuit physically.

Again, you may notice you are unable to duplicate the LTSpice design due to restricted choice of R and Cs, this means you need to do a measurement of the cutoff and tune the Rs again to match the desired cutoff.

Make full use of AD2 issued to you, Bode Plot, FTT, Waveform,... there are more than enough tools for you to debug your circuit. Refer to this page to help you solve some commonly seen issues over the past semesters. (Please check this page for your queries before sending emails to the teaching team)

| Tip | ||

|---|---|---|

| ||

|