Typical Design Flow

This section suggested the typical design flow for task 1 based on past experience.

We aim to provide a brief guide for you to kick start. There are no right or wrong approaches, (but could be poor approaches). The minor details are up to you to decide.

A. Theoretical Calculation

Based on the design specifications assigned to your team, decide what's the ideal range of the cutoff frequency.

You should keep in mind that there's no way to suppress the noise signal that it's completely gone, our task is to suppress it enough that the wanted signal can be received successfully.

A good way to determine the minimum interference level is to vary the amplitude of the noise signal, (e.g., 1/3, 1/10, 1/20/, 1/50... of the full interference amplitude), record the received signal with AD2 at different interference levels, pass them to the Opamp_file and observe the resulted PSR. Choose a proper interference amplitude based on PSR, and calculate the desired filter suppression with the equation: 20log(targer_interference_amp/full_interference_amp). The result can be used as a reference for stopband attenuation.

Aim to achieve this level of suppression first when building the circuit, and you can improve the PSR value if time is luxurious.

B. Theoretical Design

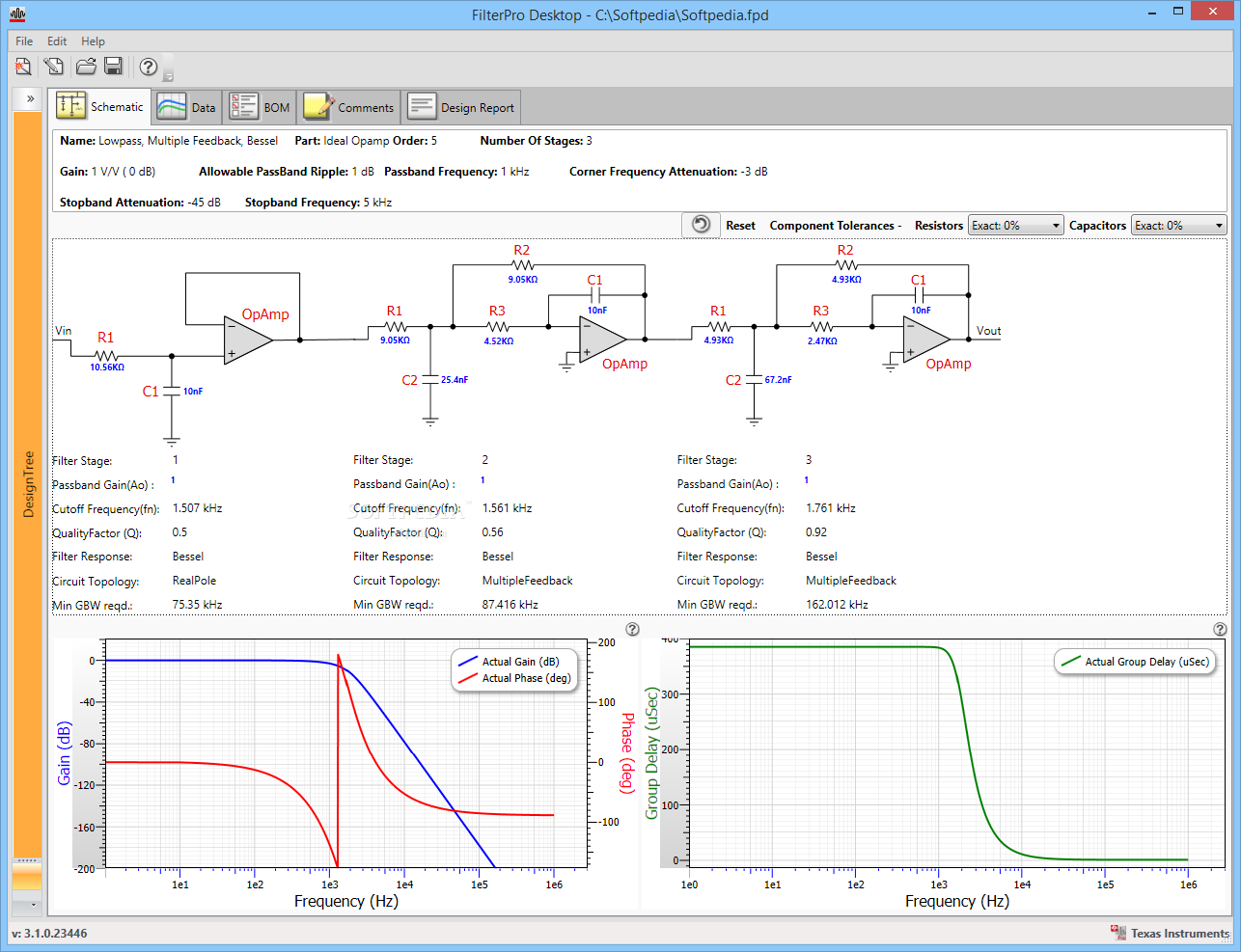

Based on the result from A, make use of FilterPro and generate your 1st theoretical Design.

Things you should spend time figuring out:

- How many orders/stages?

- Which response type to follow? What are the pros and cons?

- Do the provided OpAmps meet the Min. GBW requirements? If not, what to do? (Refer to Lab 3)

Note: The Min. GBW requirement could be insanely large, this should hint to you that this is an ideal design that serves as a reference, our goal is NOT to duplicate it on the breadboard.

C.1. LTSpice Simulation (Frequency Response)

Implement the design generated in B with LTSpice.

Helpful guides for LTSpice can be found here.